半導(dǎo)體行業(yè)發(fā)展的一大推動力,就是“始終連接設(shè)備”的爆發(fā)式增長。這些設(shè)備需要內(nèi)置的芯片,才能完成相應(yīng)的計算、通信或控制。隨著物聯(lián)網(wǎng)(IoT)擴(kuò)展到數(shù)十億計的設(shè)備,芯片制造商也需要為客戶開發(fā)出兼顧成本效益的低功耗工藝節(jié)點,以將之推向一個全新的水平。在 2020 年度的技術(shù)研討會上,臺積電就公布了該公司最新的 N12e 工藝節(jié)點的細(xì)節(jié)。

(來自:TSMC)

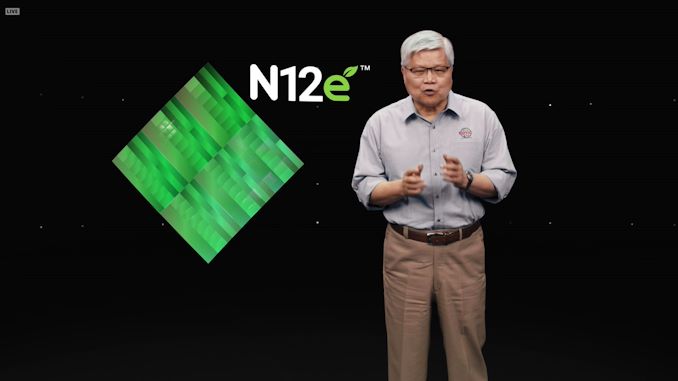

由路線圖可知,臺積電的低電功耗、低泄漏平臺,主要圍繞流行工藝節(jié)點進(jìn)行技術(shù)優(yōu)化。過去十年,臺積電在 90nm、55nm、40nm 和 22nm 節(jié)點上,都有推出過相應(yīng)的低功耗版本。

每一次的迭代,都可帶來管芯面積和功耗的降低,以及針對特定需求的其它優(yōu)化。不同的是,此前的技術(shù)都是在平面上展開,而新一代 N12e 工藝卻基于面向未來的 FinFET 。

在類似的情況下,F(xiàn)inFET 的構(gòu)建工作,將較平面晶體管要復(fù)雜得多,成本的上升已是必然。不過在 FinFET 技術(shù)帶來的制程縮放和功耗控制的優(yōu)勢面前,市場仍對其抱有濃厚的興趣。

為求穩(wěn)妥,臺積電也沒有在很早的時候就推出 FinFET 。而是在等待了數(shù)代之后,才將其最先進(jìn)的 FinFET 設(shè)計部署到了 IoT 市場,以便行業(yè)有足夠的時間來應(yīng)對設(shè)計制造上的過渡緩沖。

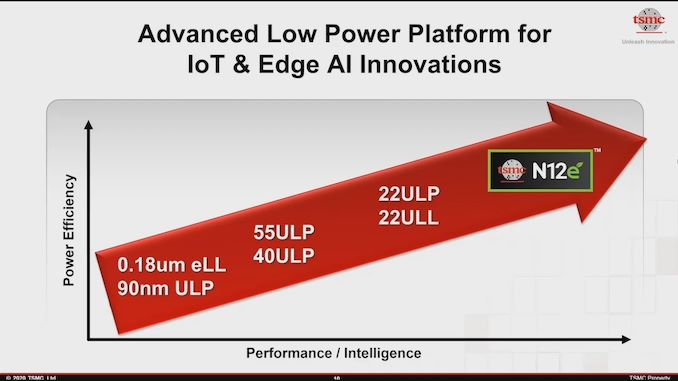

與 22ULL 工藝節(jié)點相比,臺積電承諾 N12e 可在同等功耗水平下將頻率提升至 1.49 倍、或?qū)⑼l下的功耗降低 55%,更別提增加了 1.76 倍的邏輯密度、以及支持 0.4V 的低電壓。

換言之,N12e 將臺積電面向 IoT 產(chǎn)品的芯片制程擴(kuò)展到了更低的功率范圍,并且在其它功率水平下也可帶來更好的性能表現(xiàn)。

其匯聚了臺積電在 16nm 工藝上積累的經(jīng)驗、并融入了 12FFC+ 的改進(jìn),兩者均已被廣泛應(yīng)用于高性能計算。

臺積電相信,N12e 將為 AI 加速器提供低功耗支撐,讓下一代 5G IoT 邊緣設(shè)備更加普及,從而推動語音識別、健康監(jiān)測、機(jī)器視覺等領(lǐng)域的發(fā)展。

最后,格羅方德的 12FDX 平臺,將成為 N12e 的主要競爭對手。前者建立在該公司的 12nm FD-SOI 技術(shù)之上,較同級 FinFET 設(shè)計具有更低的功耗和成本。

來源:cnBeta.COM