隨著集成電路工藝步入22 nm工藝節點,傳統的硅基金屬氧化物半導體場效應晶體管(MOSFETs)所產生的短溝道效應及低的擊穿電壓使其不再滿足高頻高功率電子器件領域的需求。近年來,金剛石基MOSFETs的相關研究引起了人們的極大關注。

金剛石具有能帶間隙寬、導熱系數高和載流子遷移率高等優良電學特性,在高溫高壓高頻高功率電子器件應用領域前景廣闊。然而,金剛石基電子器件從材料制備到器件應用這一過程的實現還存在諸多挑戰。為了推動金剛石材料電子器件的發展,加快國內外金剛石基MOSFETs的研究進程,近日,北京科技大學碳基材料與功能薄膜團隊劉金龍副研究員與早稻田大學Hiroshi Kawarada教授課題組合作的最新成果以“C-Si interface on SiO2 /(111) diamond p-MOSFETs with high mobility and excellent normally-off operation”為題發表在《Applied Surface Science》期刊上,第一作者為北京科技大學博士生朱肖華。

摘要

本文通過在(111)金剛石襯底表面沉積SiO2,在高溫還原氣體條件下構建了金剛石-硅(C-Si)界面,制備了具有C-Si導電通道的金屬氧化物半導體場效應晶體管(MOSFET),閾值電壓高達-16 V,電流密度為-167 mA/mm,溝道空穴遷移率(μFE)達到200cm2v-1s-1, 界面態密度(Dit)低至3.8×1011cm-2eV-1。通過高分辨透射電子顯微鏡(HRTEM)證明SiO2薄膜與(111)金剛石呈現連貫、平整、均勻且無應變結構,從而為器件提供了較高的溝道空穴遷移率和較低的界面態密度。電子能量損失譜(EELS)以及x射線光電子能譜(XPS)均證實了界面以C-Si鍵為主。這些結果表明,C-Si/SiO2界面在金剛石FETs具有廣闊的應用前景。

研究背景

金剛石作為一種理想的超寬禁帶半導體材料,被稱為終極半導體,是高頻大功率器件的理想材料,引起人們的廣泛關注。常規的金剛石材料屬于絕緣體, 通過硼摻雜可以實現p型導電,然而由于硼摻雜金剛石電離能較高(0.37 eV), 在室溫下很難完全電離, 而重摻雜又往往導致金剛石表面損傷, 半導體性質下降, 因此限制了金剛石半導體器件的應用發展。幸運的是,通過表面改性手段對金剛石進行功能化修飾,在其表面形成氫終止,氫化金剛石表面可產生二維空穴氣體(2DHG),使金剛石表面近表層p型導電溝道特性, 使其成為金屬-氧化物-半導體場效應晶體管(MOSFET)應用的良好選擇。

氧化后的金剛石表面將呈現高密度表面狀態,通常用于隔離襯底上的相鄰器件。氫終端(C-H)金剛石FETs憑借其載流子密度高(~1013 cm-2)、工藝簡單和高熱穩定性得到廣泛的研究。但氫終端金剛石FETs的穩定性在實際應用中仍存質疑。此外,C-H金剛石MOSFET器件由于表面2DHG的存在通常表現出耗盡型特性。事實上,增強型場效應晶體管在數字集成電路和大功率電路中具有更高的安全性和更低的功耗。目前,基于氫終端金剛石實現增強型特性的也被廣泛報道,實現的方法包括表面溝道修飾,沉積具有正電荷的柵介質,以及設計特殊的器件結構等。然而,目前所報道的增強型金剛石MOSFETs的閾值電壓(Vth)和電流密度相對較低,不適合應用于電源開關器件中。因此,將金剛石與其他材料結合,以實現高閾值電壓和高電流密度的增強型特性是急需解決的。金剛石-硅(C-Si)偶極子由于與C-H偶極子具有相似的電負性,同樣有望在金剛石表面產生2DHG。而且已經證實氧化后的硅端金剛石表面將顯示負電子親和能。SiO2是一種理想的柵介質,在MOS功率器件中具有高度穩定性,以及大禁帶寬度。SiO2/金剛石制備的C-Si界面被認為適用于高壓和高溫應用,與C-H鍵相比,金剛石中的C與SiO2中的Si直接鍵合可以提供更可靠的穩定性,更適合于半導體工業的應用。

本文研究了C-Si界面(111)金剛石MOSFET的電學特性,通過高分辨率透射電子顯微鏡(HRTEM)、電子能量損失(EELS)和x射線光電子能譜(XPS)對SiO2/(111)金剛石界面的微觀結構進行了分析。

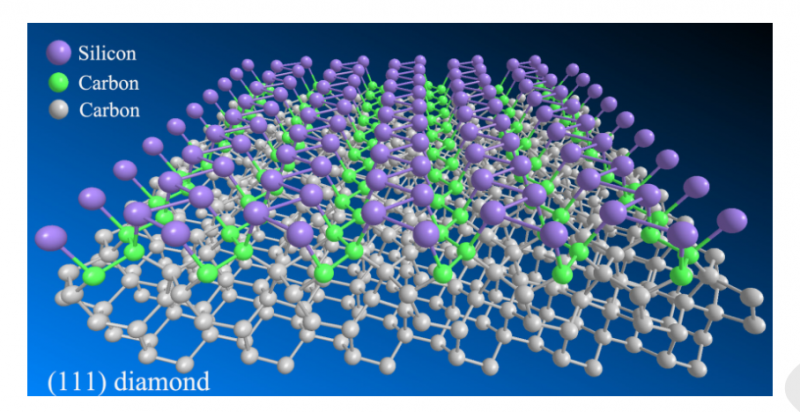

圖文

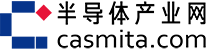

圖1:SiO2/(111)金剛石MOSFETs的示意圖。

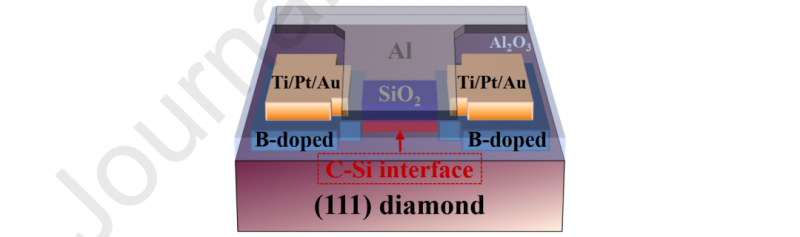

圖2:LG=4 μm, 8 μm, 10 μm 對應的SiO2/(111)金剛石MOSFETs (a,d,g) ID-VDS特性,VGS從-40 V到5 V以5 V步長變化 (b,e,h) VDS=-1 V線性坐標下的|ID|-VGS特性 (c,f,i) VDS=-30 V對數坐標下的|ID|-VGS特性 。

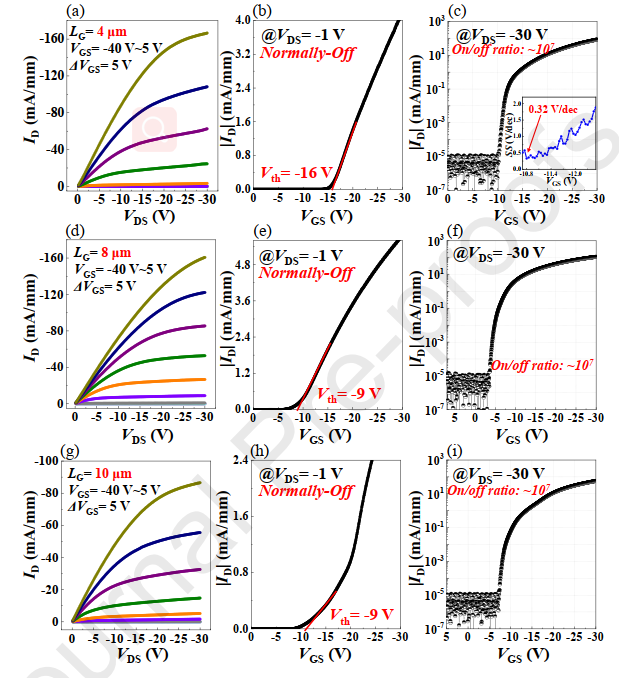

圖3:實驗中C-Si (111) 金剛石MOSFETs器件和報道的 增強型場效應晶體管的|ID| -Vth 關系對比圖。

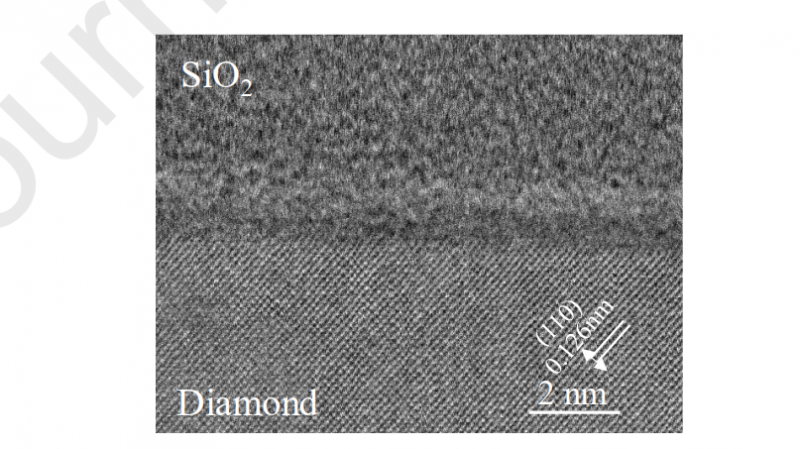

圖4:SiO2/(111)金剛石界面的HRTEM圖。

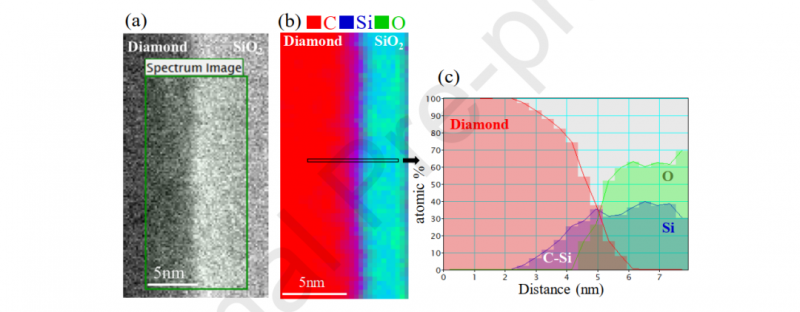

圖5:(a)SiO2/(111)金剛石界面暗場截面STEM圖像 (b) C, Si和O元素的疊加EELS map圖 (c) (b)中黑色方框對應的C, Si和O的原子百分比map圖

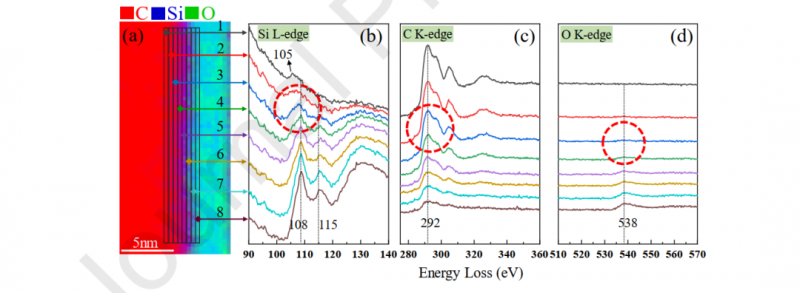

圖6: (a) C, Si和O元素的疊加EELS map圖 (b) Si L-edge (c) C K-edge (d) O K-edge在界面處的EELS能譜。紅色虛線圓圈包含界面區域的能譜特征。

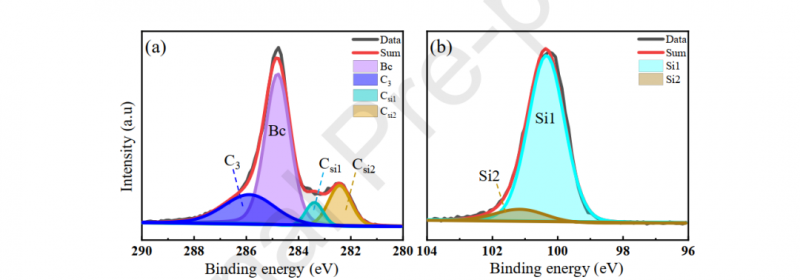

圖7:SiO2/(111)金剛石界面的(a) C1s和(b)Si2p能級的XPS譜。彩色線代表擬合曲線。

圖8:基于Pandey鏈結構的(111)金剛石表面重構的C-Si模型。

原文鏈接:https://www.sciencedirect.com/science/article/pii/S0169433222009229

作者介紹

劉金龍 北京科技大學副研究員

劉金龍,工學博士,北京科技大學副研究員。2007年本科畢業于哈爾濱工程大學;2009年碩士畢業于哈爾濱工業大學;2014年博士畢業于北京科技大學。后留校工作于北京科技大學新材料技術研究院至今。2017年至2018年,美國阿貢國家實驗室訪問學者。主要致力于功能碳材料基礎與應用研究,研究方向包括碳材料電子器件研究,單晶金剛石的大尺寸制備和應用,高功率電子器件熱管理材料及器件,功能薄膜、二維材料及等離子體表面改性,大面積高質量金剛石膜的制備與應用等。作為項目負責人先后承擔國家重點研發計劃-青年科學家項目、國家自然科學基金、北京市自然科學基金等國家與省部級項目10余項,發表學術論文60余篇,授權國家發明專利20余項,參加編著國家出版基金項目納米科學與技術叢書-《金剛石膜制備與應用》一部,獲得教育部技術發明一等獎1項,北京市科技進步三等獎1項。