由非易失性存儲器構成的交叉陣列利用物理定律的原位計算來實現高能效神經網絡是打破傳統的馮諾依曼架構計算瓶頸的關鍵路徑。然而,目前所有存儲體系的陣列計算結果需要利用大量外圍電路進行激活后才能有效執行運算任務,增加了系統功耗,成為了存算一體技術進入產業化的主要挑戰。如果利用新型電子器件本身即可實現運算結果激活,不但大幅降低功耗解決瓶頸問題,并有利于減少資源使用,將對發展更高效率更通用的新型計算技術具有重要意義。

針對這一關鍵問題,集成芯片與系統全國重點實驗室、復旦大學微電子學院周鵬教授、芯片與系統前沿技術研究院劉春森研究員創造性地開發出超快雙極性閃存器件,并實現了自激活存算一體技術。該成果利用團隊前期提出的范德華異質結超快閃存的三大要素新機理,引入雙極性二維半導體作為溝道,成功實現了高魯棒性超快雙極性閃存。通過對存儲雙極性行為的邏輯調控,實現了乘法累加操作同時完成非線性自激活輸出,顯著降低外圍電路復雜度和能耗。

北京時間2023年3月21日,相關成果以《用于自激活存內計算的超快雙極性閃存》(“An ultrafast bipolar flash memory for self-activated in-memory computing”)為題發表于國際頂尖期刊《自然-納米技術》(Nature Nanotechnology)。

復旦大學研究團隊將新型雙極性二維原子晶體集成進廣泛應用的電荷俘獲型閃存器件中,實現了雙極性閃存性能上的突破。其編程速度可達20納秒,壽命高達八百萬次,均比硅基閃存器件提高了將近三個數量級,展現出優越的存儲性能。

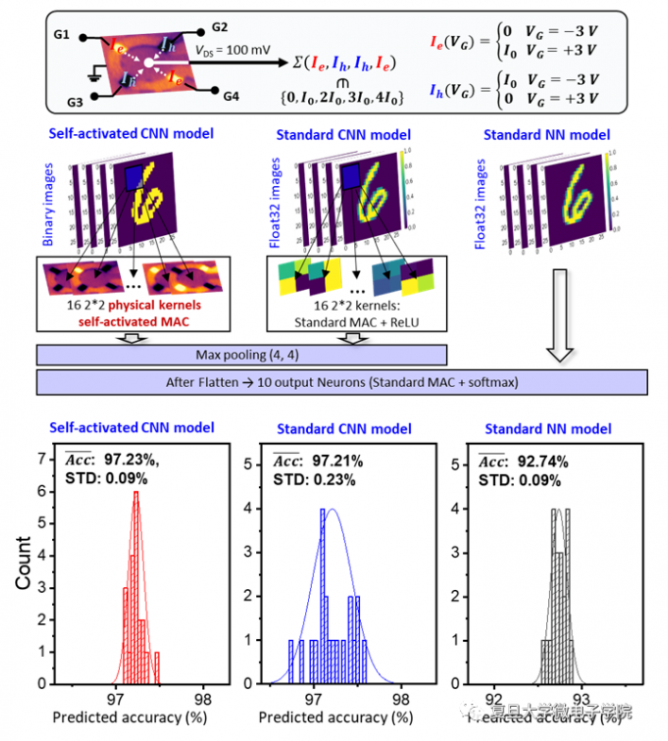

研究團隊利用二維半導體的雙極性能帶調控的特性,通過擦寫電荷俘獲層中的電子或空穴,控制形成p型/n型溝道的特性切換。柵電壓和存儲俘獲電荷的極性共同調制了溝道的開關行為,完成陣列乘積計算提升并行度。同時,并聯器件的電流輸出通過基爾霍夫定律同步實現了累加計算,大幅提高了計算效率。柵電壓和存儲電荷的極性匹配過程決定了計算結果的非線性激活輸出,省略了冗余的外部激活過程并顯著降低了由此產生的資源需求。該器件在不同的神經網絡結構下對比驗證得出高準確度,證明了自激活存算技術的高效性。

目前,利用大規模二維材料高質量生長和集成技術,基于更大尺寸的晶圓級存儲陣列正在研發中,采用協同優化方法實現組合模塊系統級開發制造,該技術將滿足低功耗高算力發展需求。相關工作得到了科技部重點研發計劃、國家自然基金委杰出青年基金、上海市基礎特區計劃、上海市啟明星等項目的資助,以及教育部創新平臺的支持。

圖超快雙極性閃存器件實現存算自激活過程示意與仿真算法驗證

原文鏈接:

https://www.nature.com/articles/s41565-023-01339-w