近日,國家信息光電子創新中心(NOEIC)和鵬城實驗室的光電融合聯合團隊完成2Tb/s硅光互連芯粒(chiplet)的研制和功能驗證,在國內首次驗證了3D硅基光電芯粒架構,實現了單片最高達8×256Gb/s的單向互連帶寬。

2Tb/s 硅基3D集成光發射芯粒

隨著人工智能應用的快速發展,AI算力系統對于高效能互連技術的需求呈現爆發性增長態勢。為了滿足這一挑戰,業界正大力研發更大容量、更高速率、更高集成度的硅基光互連芯片解決方案,把硅光收發芯片直接集成到計算芯片附近或同一封裝內,極大地減少信號傳輸的延遲和功耗,從而顯著提升算力系統的整體性能。然而,面向下一代單通道200G以上(200G per lane)的光接口速率需求,硅光方案在速率、功耗、集成度等方面面臨著巨大挑戰。

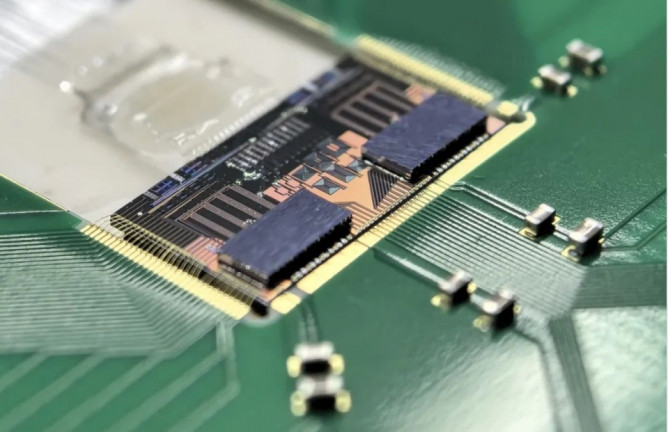

該團隊在2021年1.6T硅光互連芯片的基礎上,進一步突破了光電協同設計仿真方法,研制出硅光配套的單路超200G driver和TIA芯片, 并攻克了硅基光電三維堆疊封裝工藝技術,形成了一整套基于硅光芯片的3D芯粒集成方案。

硅光互連芯粒的側向顯微鏡結構

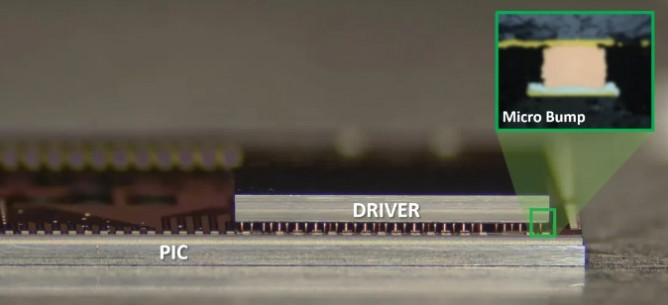

該方案充分利用了硅光與CMOS封裝工藝兼容的特點,相比于傳統wirebond方案,3D芯粒能解決電芯片與光芯片間高密度、高帶寬電互連的困難,顯著降低射頻信號在光-電芯片互連過程中的嚴重衰減。經系統傳輸測試,8個通道在下一代光模塊標準的224Gb/s PAM4光信號速率下,TDECQ均在2dB以內。通過進一步鏈路均衡,最高可支持速率達8×256Gb/s,單片單向互連帶寬高達2Tb/s。

8×224Gb/s硅基光發射芯粒輸出眼圖

據介紹,該工作充分展現了3D集成硅光芯粒的優越互連性能,以及聯合團隊的領先自主研發水平。該成果將廣泛應用于下一代算力系統和數據中心所需的CPO、NPO、LPO、LRO等各類光模塊產品中,為國內信息光電子技術的率先突圍探索出可行路徑。

目前,全球量產硅光芯片產品的主流傳輸速率為800Gb/s,1.6Tb/s產品剛剛發布。此次,由國家信息光電子創新中心等單位自主研發的2Tb/s硅光芯粒樣品,已達到國際先進水平。預計近期可以實現高端硅光芯片的批量商用。

(來源:國家信息光電子創新中心)